在基于GD32系列微控制器的嵌入式系统设计中,晶振电路是确保系统稳定运行的核心。一个设计良好的晶振电路为MCU提供精确的时钟源,直接影响程序的执行时序、通信接口的波特率精度以及外设模块的可靠性。本文旨在为电子技术开发者,特别是21ic电子技术开发论坛的工程师们,提供一个清晰、实用的GD32晶振电路设计指南。

1. 晶振电路的基本构成与选择

GD32 MCU通常支持两种时钟源:外部高速晶振和外部低速晶振。

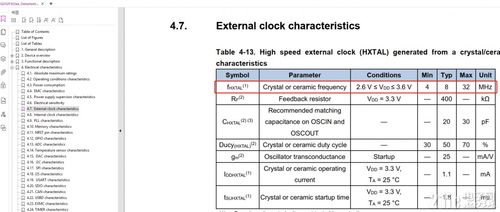

- 外部高速晶振:为主系统提供时钟,频率范围常见为4MHz~32MHz(具体需查阅对应型号的数据手册)。这是系统运行、外设工作的主要时钟源。

- 外部低速晶振:通常为32.768kHz,主要用于实时时钟模块,提供精确的计时基准。

晶振选择关键参数:

频率:根据系统需求选择。8MHz和12MHz是常见选择,平衡了性能和通用性。

负载电容:这是晶振最重要的参数之一,标注为CL,典型值如12pF, 20pF等。它决定了外部匹配电容的值。

* 精度:根据应用对时钟精度的要求选择,如±10ppm、±20ppm等。通信应用(如USB、UART)通常要求更高的精度。

2. 标准电路设计与元器件计算

一个典型的外部高速晶振电路如下图所示(概念示意):

`

VDD (3.3V)

|

[Rf] (可选,1MΩ典型值)

|

+---- XO (晶振输出) ----||---- OSC_IN (MCU引脚)

| C1

[晶振] |

| GND

+---- XI (晶振输入) ----||---- OSC_OUT (MCU引脚)

C2

|

GND`

晶振:核心器件。

负载电容C1, C2:其值由晶振要求的负载电容CL、电路板寄生电容(Cs,通常估算为2~5pF)和MCU引脚输入电容(Ci,详见数据手册)共同决定。计算公式为:

`

C1 = C2 = 2 (CL - Cs) - Ci

`

例如,若晶振CL=20pF,估算Cs=3pF,Ci=5pF,则C1=C2 = 2(20-3)-5 = 29pF。可选择最接近的标准值,如22pF并联6.8pF,或直接使用27pF或33pF。这是设计的关键步骤。

- 反馈电阻Rf:对于GD32,内部通常已集成,外部可省略。若需要,可并联一个1MΩ~10MΩ的大电阻,有助于起振稳定。具体请参考对应型号的参考手册。

- 布局布线要点:

- 最短走线:将晶振、电容尽可能靠近MCU的OSCIN和OSCOUT引脚放置。

- 包围地线:用接地铜皮包围整个晶振电路,并与主地平面通过单点连接,以隔离噪声。

- 远离噪声源:远离高频信号线、电源开关电路、磁性元件等。

- 避免过孔:连接晶振和电容的走线尽量避免使用过孔。

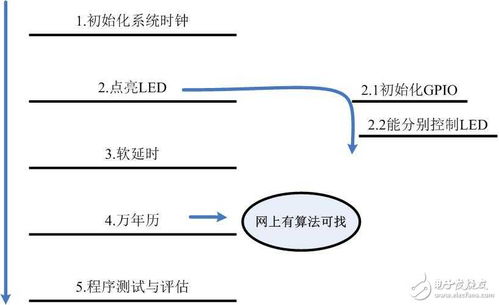

3. 针对GD32的特殊注意事项

- 启动配置:GD32的时钟系统非常灵活。上电后,默认使用内部RC振荡器。需要在软件初始化阶段,通过配置时钟树寄存器,使能并切换至外部高速晶振作为系统时钟源。务必在代码中检查外部晶振是否就绪(通过时钟控制状态寄存器)。

- 低功耗模式:在进入某些低功耗模式时,外部高速晶振可能会被关闭以节能。唤醒后,需要根据手册描述重新使能并等待稳定。

- 硬件设计验证:

- 最直接的验证方法是使用示波器探头(建议使用10X衰减档,以减小探头电容影响)测量OSC_IN引脚波形。应观察到干净、幅值充足(接近VDD)、频率准确的正弦波或类正弦波。

- 如果晶振不起振,检查:电源是否稳定、电容值是否匹配、焊接是否良好、MCU相关引脚配置是否正确(应配置为外部振荡器模式,而非GPIO)。

- 备选方案:对于时钟要求不高的应用,GD32的高精度内部RC振荡器(如8MHz/108MHz等)是可靠且节省成本和PCB空间的方案。但若需USB或高精度定时,外部晶振仍是首选。

4. 外部低速晶振电路

设计原则与高速晶振类似,但因其频率低、增益小,对负载电容和布局更为敏感。

- 负载电容CL通常为12.5pF。

- 同样使用两个匹配电容C1和C2,计算方式相同。

- 走线应更加精简。

###

设计GD32的晶振电路,关键在于:根据数据手册选择合适参数的晶振,精确计算并选用匹配的负载电容,以及进行严谨的PCB布局布线。遵循以上原则,可以最大程度地保障系统时钟的稳定与可靠,为整个嵌入式项目的成功奠定坚实基础。在实际开发中,务必结合具体GD32型号的《数据手册》和《参考手册》进行最终设计定稿。